## SPQ16R5P40WP

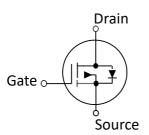

### 40V P-Channel MOSFET

- Advanced Trench Device Design and Processes

- High Reliability Capability

- Sampled CP Probing and Inking

| Electrical Characteristics in C/P Test (T」 at 25 °C) |                                   |                     |      |      |    |                                            |

|------------------------------------------------------|-----------------------------------|---------------------|------|------|----|--------------------------------------------|

| $V_{(BR)DSS}$                                        | Drain-Source Breakdown Voltage    | _                   |      | -40  | ٧  | $V_{GS} = 0V, I_D = -250 \mu A$            |

| R <sub>DS(ON)</sub>                                  | Static Drain-Source On-Resistance | _                   | 12.5 | 16.5 | mΩ | $V_{GS} = 10V, I_D = -1A^{(2)}$            |

| R <sub>DS(ON)</sub>                                  | Static Drain-Source On-Resistance | _                   | 17.6 | 21   | mΩ | $V_{GS} = 4.5V, I_D = -1A(2)$              |

| V <sub>GS (th)</sub>                                 | Gate Threshold Voltage            | -2.5                | I    | -1.2 | >  | $V_{DS} = V_{GS}$ , $I_D = -250 \mu A$     |

| I <sub>DSS</sub>                                     | Drain-to-Source Leakage Current   | -1                  |      |      | μΑ | V <sub>DS</sub> =-40V, V <sub>GS</sub> =0V |

| I <sub>GSS</sub>                                     | Gate-to-Source Leakage Current    | -100                | _    | 100  | nA | V <sub>DS</sub> =0V, V <sub>GS</sub> =±20V |

| T <sub>J</sub> , T <sub>STG</sub>                    | Operating and Storage Temperature | -55°C to 150°C Max. |      |      |    |                                            |

| Mechanical Data                    | Die Drawing                                                                                 |           |  |

|------------------------------------|---------------------------------------------------------------------------------------------|-----------|--|

| Chip Size <sup>(2)</sup>           | 1764 μm X 1270 μm                                                                           | 1270.1 um |  |

| Gate Pad Size                      | 150 µm X 150 µm                                                                             | 1438      |  |

| Source Pad Size                    | 1436µm X 1070 µm                                                                            | 436.05 um |  |

| Scribe Line Width                  | 60 µm                                                                                       |           |  |

| Wafer Thickness                    | 150 µm                                                                                      | 1070.1 um |  |

| Wafer Diameter                     | 200 mm                                                                                      | 1763.9 um |  |

| Gross Die                          | 11782 EA                                                                                    |           |  |

| Source Metallization               | Al-Cu (4µm typical)                                                                         | 150 um    |  |

| Drain Metallization                | Ti-Ni-Ag                                                                                    | 150 um    |  |

| Passivation                        | SiN                                                                                         |           |  |

| Recommended Storage<br>Environment | Store in original container, in dry nitrogen, 6 months at ambient temperature of 23°C ± 3°C |           |  |

<sup>(1)</sup> Pulse Width tp = < 1 mS, Duty Cycle < 2%.

<sup>(2)</sup> Chip size not include scribe line.

# SPQ16R5P40WP

| Specific Assembly Info           | Die Drawing  |           |

|----------------------------------|--------------|-----------|

| Package Type                     | DFN5*6       | 1270.1 um |

| Die Attach Method                | Soft solder  | 36.05 um  |

| Soft Solder Composition          | Pb,Sn,Ag     | 1070.1 um |

| Gate Wire Bonding                | Cu, 2 mil x1 | 1763.9 um |

| Source Wire Bonding              | Al Ribbon    | 150 um    |

| Molding Compound<br>Manufacturer | G700HF       | 150 um    |

| Solder Plating Composition       | Pure Tin     |           |

| Position |         |        | Bonding Diagram Top View |

|----------|---------|--------|--------------------------|

|          | X (μm)  | Υ (μm) | TOP                      |

| ZERO     | 0       | 0      | S2                       |

| ТОР      | 1763.9  | 1270.1 | G2<br>G1                 |

| S1       | 100     | 100    |                          |

| S2       | 1536.05 | 1170.1 | S1                       |

| G1       | 1586.05 | 560.05 | ZERO                     |

| G2       | 1736.05 | 710.05 |                          |

### SPQ16R5P40WP

Version: 1.0

| $I_{DSS}$                         | Drain-to-Source Leakage Current   | -1   | _ | _    | μΑ | $V_{DS}$ =-40V, $V_{GS}$ =0V                |

|-----------------------------------|-----------------------------------|------|---|------|----|---------------------------------------------|

| I <sub>GSSF</sub>                 | Gate-to-Source Leakage Current    | _    | _ | 100  | nA | V <sub>DS</sub> =0V, V <sub>GS</sub> =+20V  |

| I <sub>GSSR</sub>                 | Gate-to-Source Leakage Current    | -100 | _ | _    | nA | V <sub>DS</sub> =0V, V <sub>GS</sub> =-20V  |

| BV <sub>DSS</sub>                 | Drain-Source Breakdown Voltage    | _    | _ | -40  | V  | V <sub>GS</sub> =0V, I <sub>D</sub> =-250μA |

| BV <sub>DSS</sub>                 | Drain-Source Breakdown Voltage    | _    | _ | -40  | V  | $V_{GS} = 0V$ , $I_D = -1mA$                |

| R <sub>DS(ON)</sub>               | Static Drain-Source On-Resistance | _    | _ | 18   | mΩ | V <sub>GS</sub> =-10V, I <sub>D</sub> =-11A |

| R <sub>DS(ON)</sub>               | Static Drain-Source On-Resistance | _    | _ | 25   | mΩ | V <sub>GS</sub> =-4.5V, I <sub>D</sub> =-7A |

| V <sub>GS (th)</sub>              | Gate Threshold Voltage            | -2.5 | _ | -1.2 | V  | $V_{DS} = V_{GS}$ , $I_D = -250 \mu A$      |

| $V_{SD}$                          | Body Diode Forward Voltage        | -1.2 | _ | _    | V  | V <sub>GS</sub> =0V, I <sub>SD</sub> =-11A  |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storage Temperature | -55  | _ | 150  | °C |                                             |

#### Disclaimer:

JUNSHINE does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

JUNSHINE reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

JUNSHINE makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, JUNSHINE disclaims (1) any and all liability arising out of the application or use of any product, (2) any and all liability, including without limitation special, consequential or incidental damages, and (3) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

JUNSHINE products, except as expressly indicated in writing, are not designed for use in medical, life-saving, or life-sustaining applications, or for any other application in which the failure of the JUNSHINE product could result in personal injury or death. Customers using or selling JUNSHINE products not expressly indicated for use in such applications do so at their own risks.

Resale of JUNSHINE products with statements different from or beyond the parameters stated by JUNSHINE for that product or service voids all express or implied warrantees for the associated JUNSHINE product or service and is unfair and deceptive business practice. JUNSHINE is not responsible or liable for any such statements.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of JUNSHINE. Product names and markings noted herein may be trademarks of their respective owners.

JUNSHINE IS A FULLY OWNED SUBSIDIARY OF Wuxi XICHANWEIXIN Semiconductor Co., Ltd.

Address: Floor 5, D2 Building, No. 200, Linghu Blvd., Wuxi, Jiangsu, China